FCLK, UCLK, IO Die, Fabric… O que tudo isso significa no Ryzen 9000? Veja nosso guia!

Apesar da nova arquitetura Zen5, os Ryzen 9000 são bastante semelhantes aos seus predecessores, mantendo o mesmo IO Die e topologia geral, o que significa que os limites para overclock de memória e desempenho do fabric deveriam ser os mesmos… Acontece que eles não são e nesse artigo, vamos explanar o que é o que dentro da CPU, tudo para te ajudar chegar no limite!

Começando nossa introdução sobre toda a sopa de letrinhas de siglas e abreviações que devem fazer parte dos pesadelos de quem não está familiarizado com isso! 😀

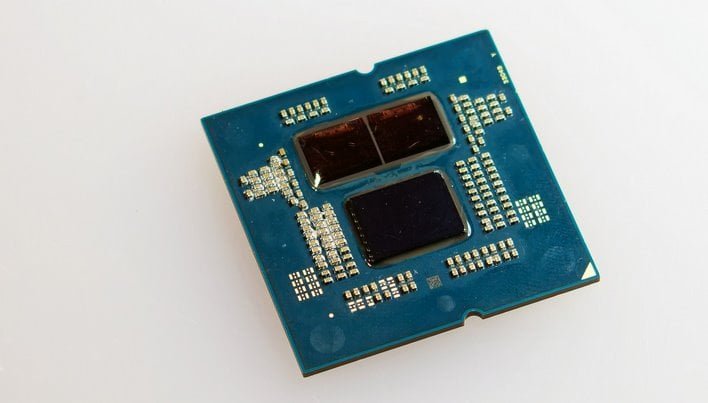

Abaixo, temos um diagrama de bloco de como é o SoC das CPUs Ryzen 7000 e 9000, como os dies, compostos por CCDs, que são onde ficam os núcleos da CPU e o IO Die (cIOD), que é onde estão controladores de memória, vídeo integrado, PCIe e demais recursos de IO, são conectados.

Para fazer a ligação entre esses dies, temos o ‘Infinity Fabric’ (IF), que faz a interconexão das partes via package, cuja frequência de funcionamento é chamada de fclk, entretanto, para que essa comunicação aconteça, existem dentro do CCD e do cIOD circuitos conhecidos como PHY, que permitem fazer essa conexão externa entre diferentes dies por meio do package. Guardem esse termo, ele será importante mais adiante! 😉

Cabe a observação que o IF é uma espécie de intermediário entre os núcleos da CPU e a memória, de forma que se esse barramento tiver menos banda do que a memória pode oferecer, os ganhos por usar RAMs rápidas tendem a ser limitados, como costumamos observar nos Ryzen 7000 e 9000.

Praticamente todas arquiteturas de computação moderna usam lógica síncrona em sua construção, ou seja, com blocos funcionais que mudam de estado sincronizados a um mesmo sinal de clock, contudo, nem todos os circuitos trabalham na mesma frequência, o que significa que a princípio, eles são incapazes de conversar entre si, sendo necessário um bloco para fazer a sincronia, o tal do SyncFIFO que aparece no diagrama do SoC.

É claro que isso tem um custo em latência e é por isso que manter uma proporção exata entre a frequência do FCLK e MEMCLK, que é o clock das memórias, como FCLK 2200 com DDR5-6600, ou seja, 1:3, resulta em menor latência do que FCLK 2200 e DDR5-6400.

Ainda dentro do cIOD temos a controladora de memória (UMC), sendo o bloco responsável por lidar com aspectos de temporização, os famosos timings e as requisições de acesso pela CPU, que trabalha em uma frequência chamada de UCLK, que pode trabalhar sincronizada ao MEMCLK (UCLK=MEMCLK) ou na metade da sua frequência (UCLK=MEMCLK/2).

Vale lembrar que para UCLK=MEMCLK, a frequência máxima das memórias acaba geralmente limitada em 6400 MT/s, com poucos exemplares chegando aos 6600 MT/s com estabilidade, enquanto com UCLK=MEMCLK/2, em tese é possível chegar aos 8000 MT/s ou mais, contudo, nesse modo, é importante atingir a máxima frequência possível nas memórias para compensar a controladora mais lenta.

As PHYs não estão presentes apenas na comunicação entre CCD e cIOD, esses circuitos também são necessários para fazer a conexão dos chips de memória com o UMC, fazendo o “trabalho sujo” da comunicação elétrica entre as partes e é aí que aqueles ajustes de impedância e terminações atuam, fazendo a diferença na integridade de sinal e por consequência, na estabilidade do sistema, especialmente com frequências de memória mais elevadas.

É bom lembrar que um bom tempo atrás, a AMD soltou uma atualização de AGESA incluindo o tal Nitro Mode, que permitiu aos Ryzen 7000 atingir os 8000 MT/s nas memórias. Apesar de não terem disponibilizado uma explicação clara do que faz cada ajuste do Nitro, na realidade, esses parâmetros permitem manipular certos “timings” que existem para manter a integridade dos dados na comunicação entre o UMC e suas respectivas PHYs, permitindo atingir frequências mais elevadas na memória, ainda que com uma pequena penalidade de latência em alguns casos.

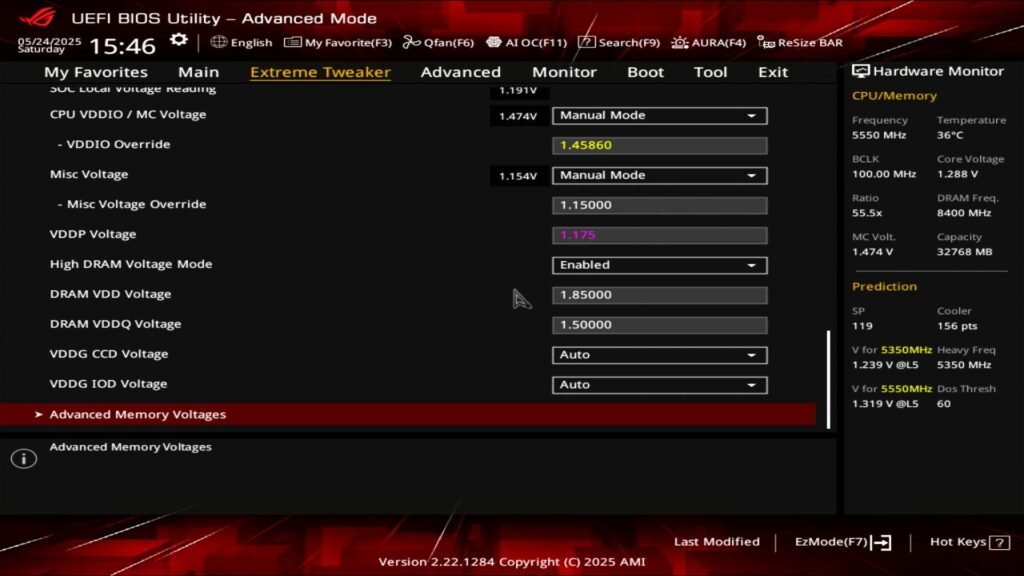

Mas a “sopa de letrinhas“ não para por aí, já que na BIOS da placa-mãe temos uma série de ajustes, especialmente de tensão, que podem ser um tanto quanto confusos por nem sempre darem pistas diretas sobre o que está sendo alterado e qual vai ser a sua influência na CPU, então, vamos ver qual a influência desses ajustes em cada um desses blocos!

CPU Core Voltage:

Como o nome deixa claro, trata-se da tensão de alimentação dos núcleos da CPU e influência diretamente na frequência da CPU, além do consumo. Normalmente, não impacta as memórias e os demais dominios de frequência do SoC.

CPU SOC Voltage:

Essa é a tensão de alimentação do cIOD, mas é bom lembrar que assim como existem diferentes domínios de frequência, o mesmo também vale para as tensões, com nem todos os blocos usando diretamente a tensão do VDDSOC.

Na hora do overclock, o VDDSOC lida diretamente com o UCLK e é uma boa explicação do porquê geralmente é possível rodar com tensão mais baixa aqui enquanto usando o modo UCLK=MEMCLK/2, mesmo com memória em 8000 MT/s ou mais. Por mais contra-intuitivo que seja, esse ajuste tem pouco peso na frequência máxima de memória ou mesmo do FCLK.

CPU VDDIO:

Esse parâmetro tem certa importância no overclock de memória, geralmente sendo necessário subir essa tensão conforme se aumenta o MEMCLK, entretanto, existe grande variação entre diferentes exemplares de CPU, inclusive com alguns apresentando erros nos testes de estabilidade no caso de se exagerar na dose. Como regra geral, é possível fazer até 6400 MT/s com 1.35V ou menos e 8000 MT/s com algo entre 1.4V e 1.45V.

VDDP ou CLDO_VDDP:

Tensão dos PHYs de memória, a qual pode ser de vital importância para quem tiver buscando voar alto no MEMCLK e assim como o VDDIO, é um parâmetro com grande variação entre amostras. Na média e em casos mais extremos, ele não costuma escalar acima de 1.175V, isso para frequências de memória acima de DDR5-8000.

VDDG CCD E IOD:

Essa dupla de parâmetros se referem as tensões dos PHYs do Infinity Fabric, que ligam o cIOD aos CCDs, onde por óbvio, o VDDG CCD está do lado da CPU e o VDDG IOD está do lado do cIOD. Caso esteja usando uma CPU com 2 CCDs, é possível ajustar separadamente as tensões dos PHYs de cada CCD.

Esses parâmetros podem ser ajustados ao se fazer overclock no FCLK, podendo ajudar com instabilidades pontuais, ainda que muito raramente isso sirva para ir além do limite da CPU, por exemplo, um exemplar que não passa no post com mais de 2166 MHz no FCLK, muito provavelmente vai continuar com essa mesma limitação, mesmo ajustando os VDDGs.

Tá, mas e agora?

Conhecendo os blocos funcionais da CPU e também como cada uma dessas partes respondem aos diferentes de ajustes de tensão disponíveis, fica mais fácil ser bem-sucedido na hora do overclock, já que o que antes era feito na base do chutômetro quando as coisas iam mal, agora pode ser feito de maneira mais consciente, sabendo no que está mexendo.

Apenas como um exemplo do que é possível fazer, nos screenshots abaixo temos o Ryzen 7 9700X completando vários testes da suíte do 3dmark com memória rodando a DDR5-8400 CL32, sendo esse o limite para esse exemplar com temperatura ambiente, podendo ir além com o uso de chiller ou soluções ainda mais agressivas.

É claro que por mais bem ajustado que esteja, existem outros fatores limitantes que podem estar fora do controle direto do usuário, como a qualidade da amostra da CPU, placa-mãe e temperatura ambiente, então, como sempre, overclock depende de sorte e da boa e velha loteria do silício.

Muito boa a sua publicação, estou com uma a620ms, que viso fazer OC no 8700g, estou visando memorias baratas para fazer OC vengeance 5200mhz cl40 para melhorar os times e a frequencia para 6400